# F.Y.B.Sc.(IT) Syllabus: Fundamentals of Digital Computing

| Unit – I  | Data and Information                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Onii – i  | Peatures of Digital Systems, Number Systems-Decimal, Binary, Octal, Hexadecimal and their inter conversions, Representation of Data: Signed Magnitude, one's complement and two's complement, Binary Arithmetic, Fixed point representation and Floating point representation of numbers.  Codes  BCD, XS-3, Gray code, hamming code, alphanumeric codes (ASCII, EBCDIC, UNICODE), Error detecting and error correcting codes. |

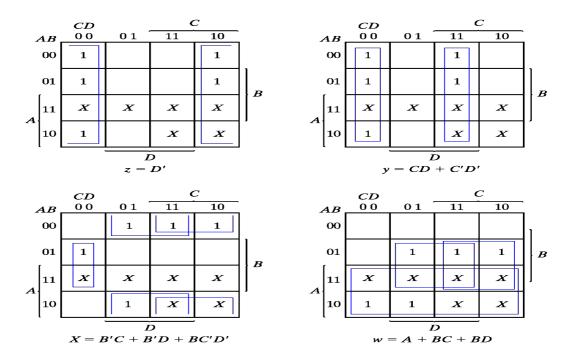

| Unit- II  | Boolean Algebra:                                                                                                                                                                                                                                                                                                                                                                                                               |

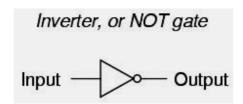

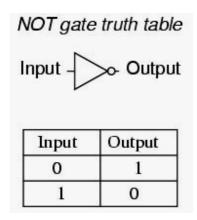

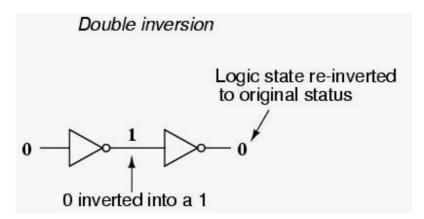

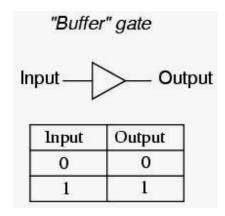

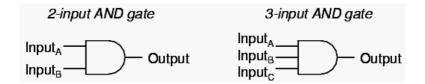

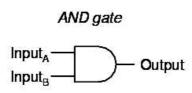

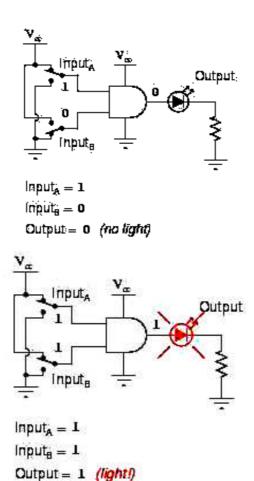

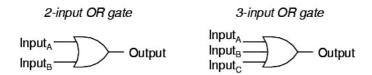

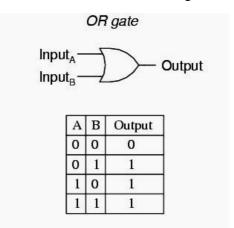

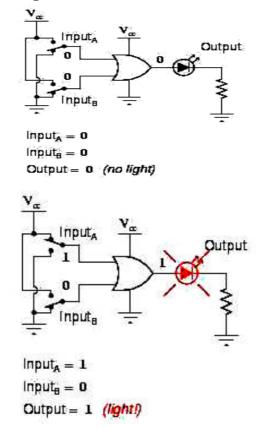

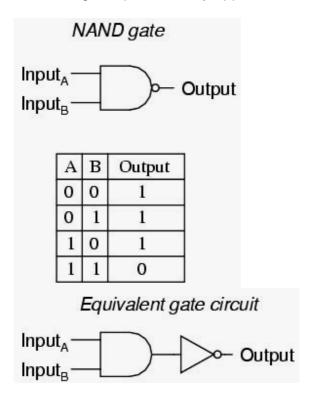

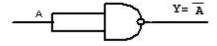

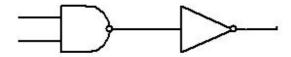

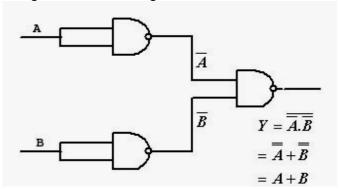

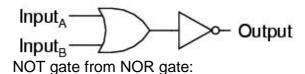

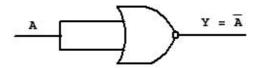

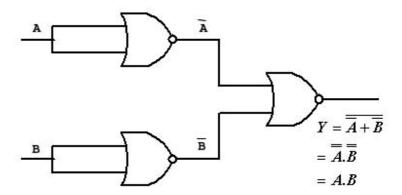

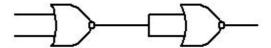

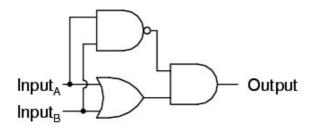

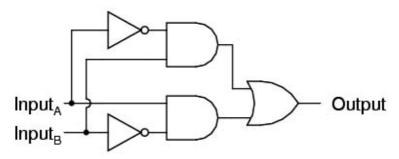

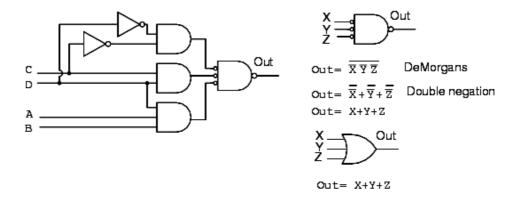

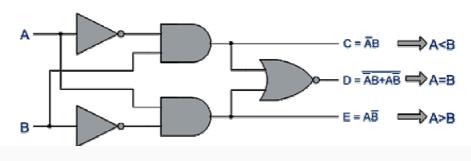

|           | Basic gates (AND, OR, NOT gates), Universal gates (NAND and NOR gates), other gates (XOR, XNOR gates). Boolean identities, De Morgan Laws.                                                                                                                                                                                                                                                                                     |

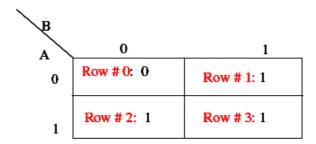

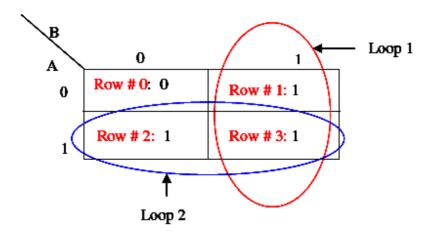

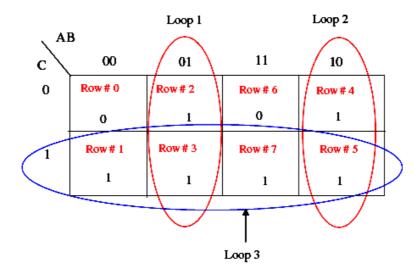

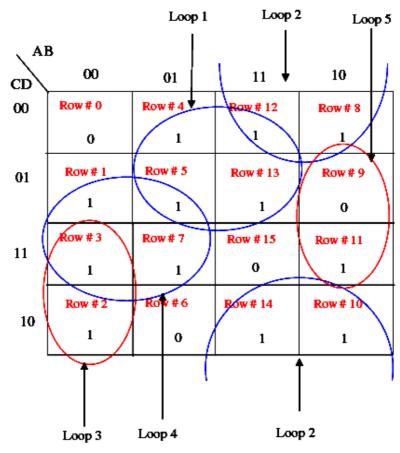

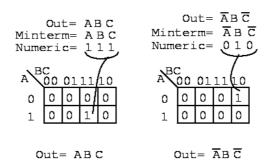

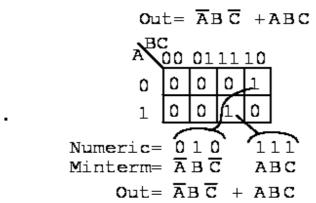

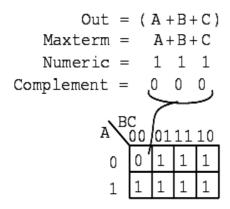

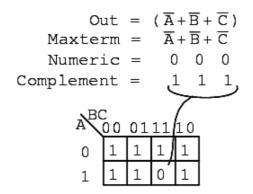

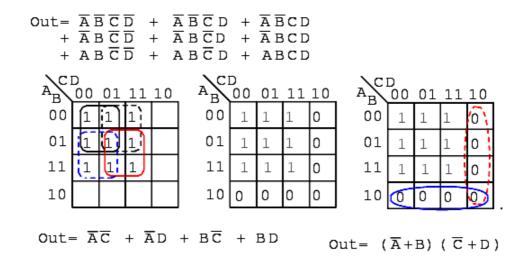

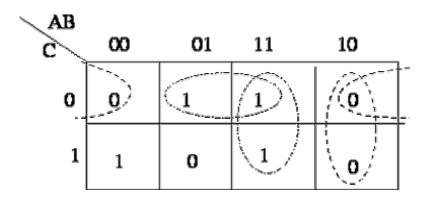

|           | Karnaugh maps:                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | SOP and POS forms, Quine McClusky method.                                                                                                                                                                                                                                                                                                                                                                                      |

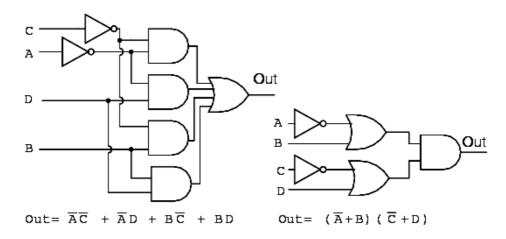

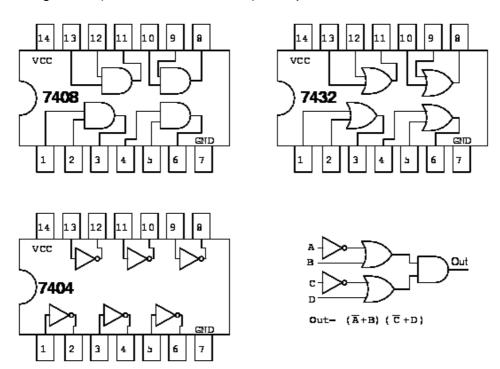

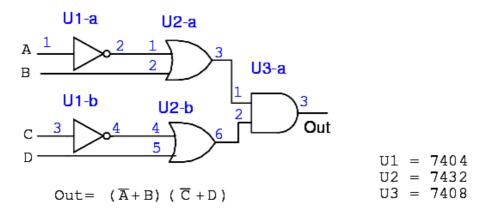

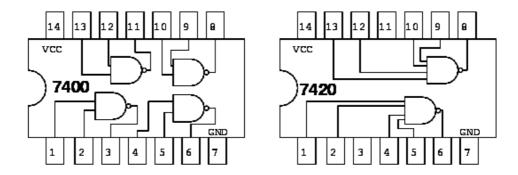

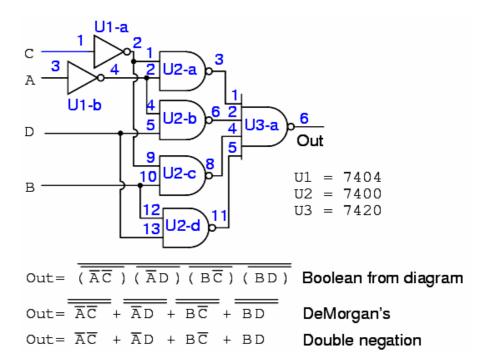

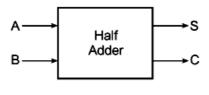

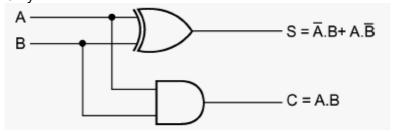

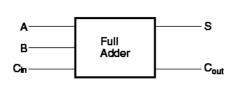

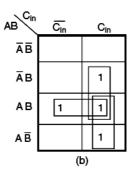

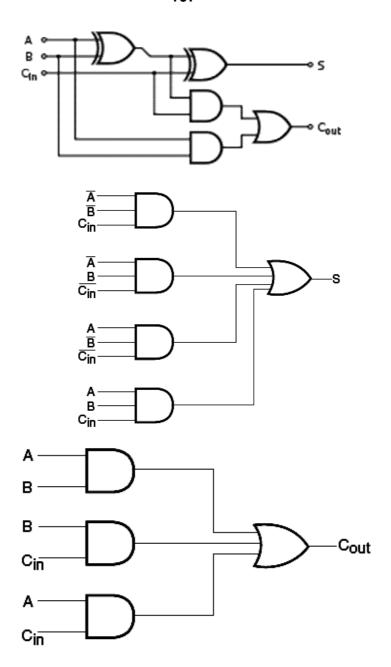

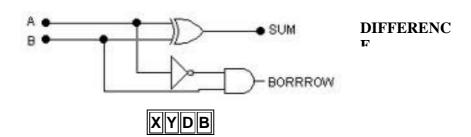

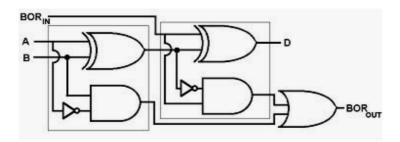

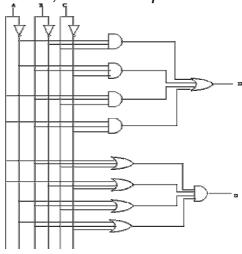

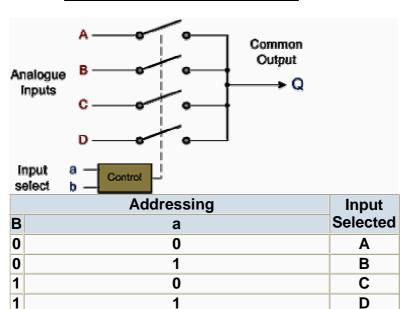

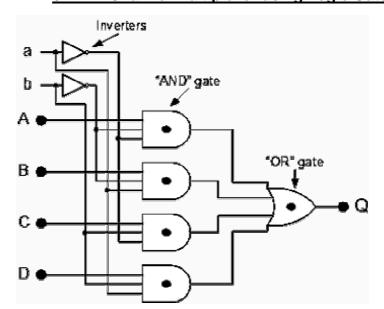

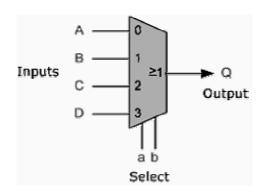

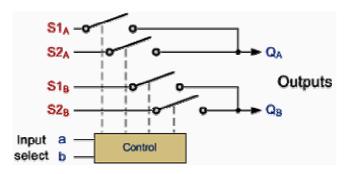

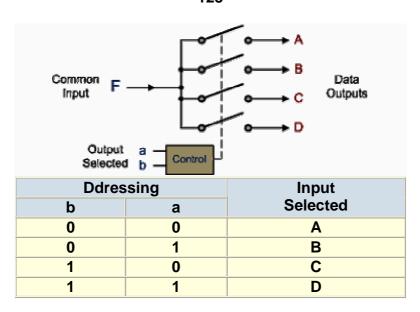

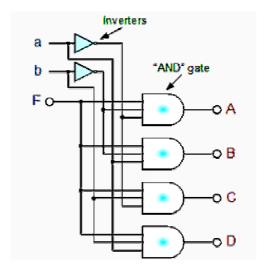

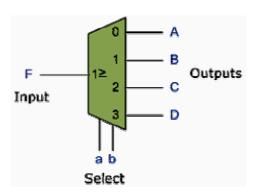

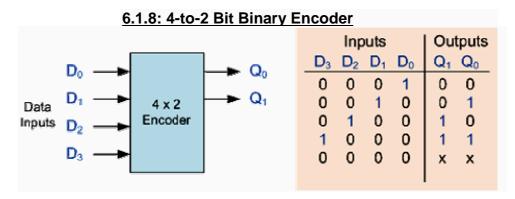

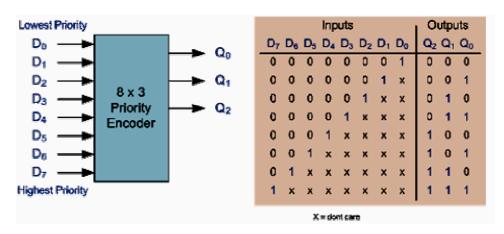

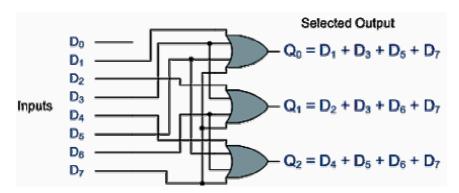

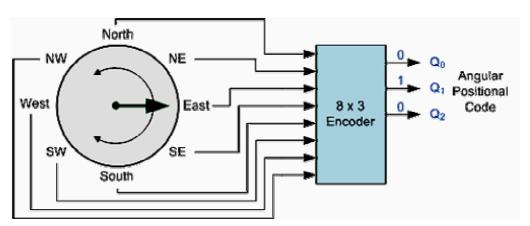

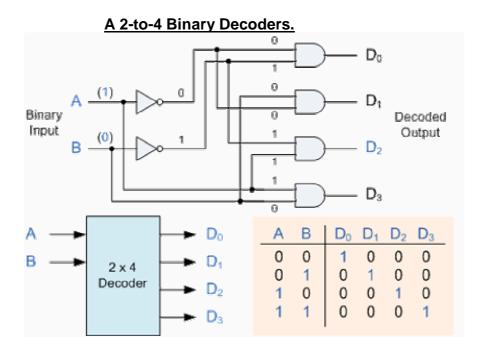

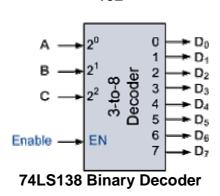

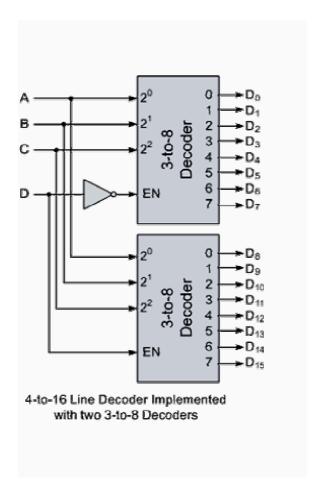

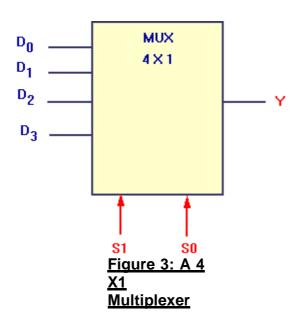

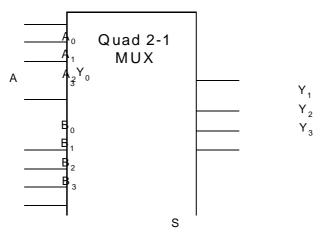

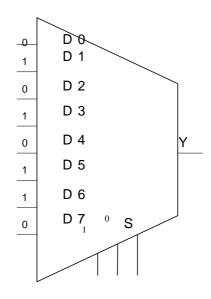

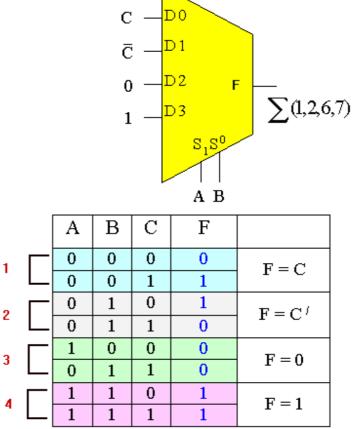

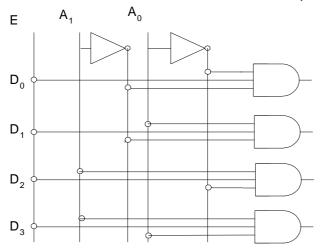

| Unit -III | Combinational Circuits:  Half adder, full adder, code converters, combinational circuit design, Multiplexers and demultiplexers, encoders, decoders, Combinational design using mux and demux.                                                                                                                                                                                                                                 |

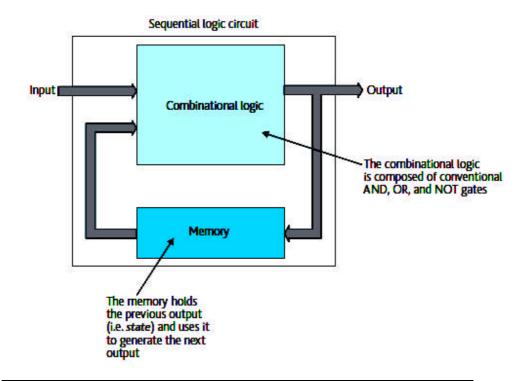

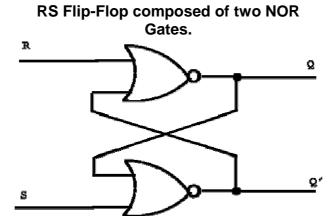

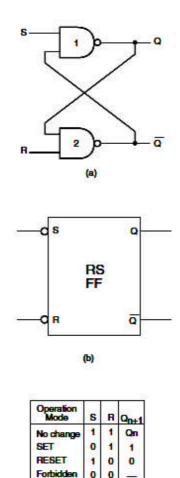

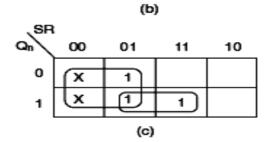

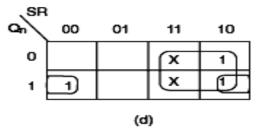

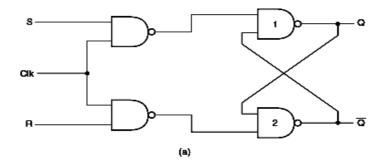

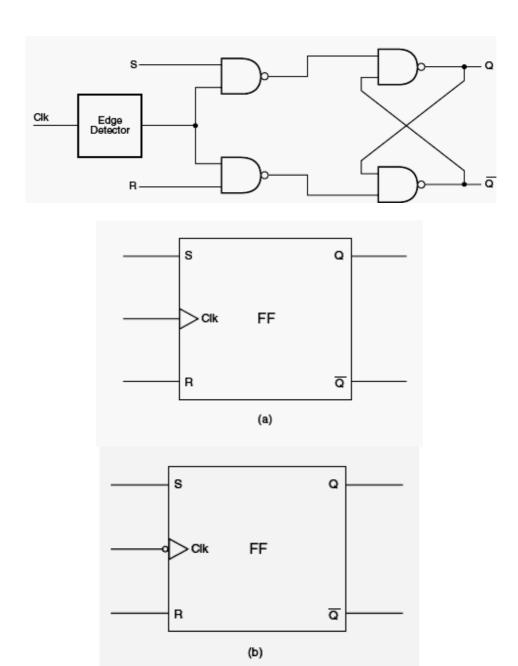

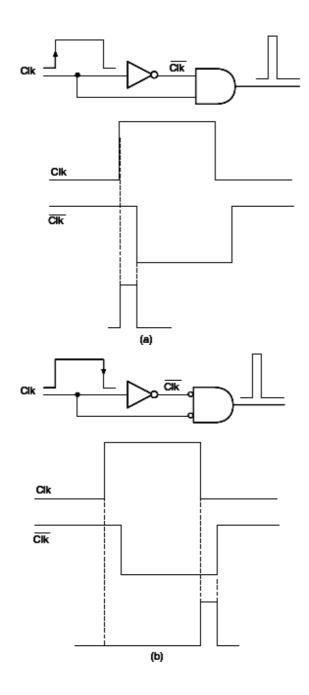

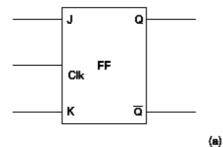

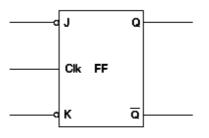

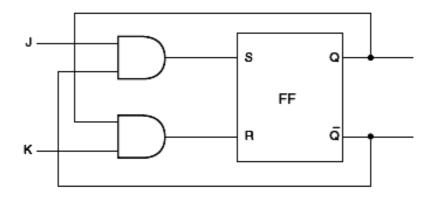

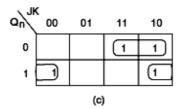

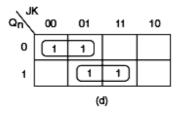

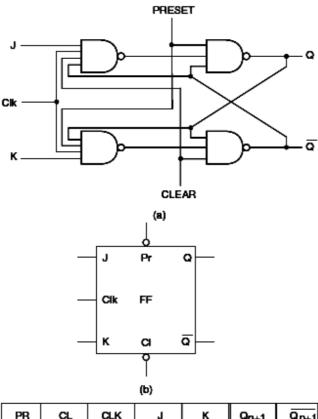

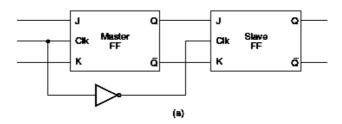

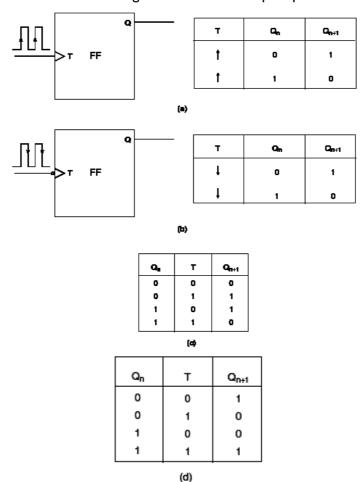

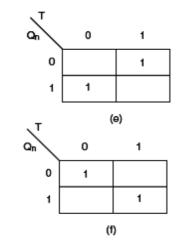

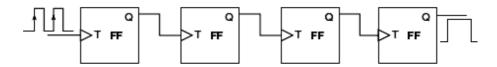

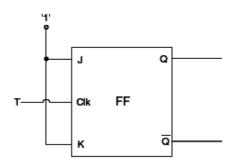

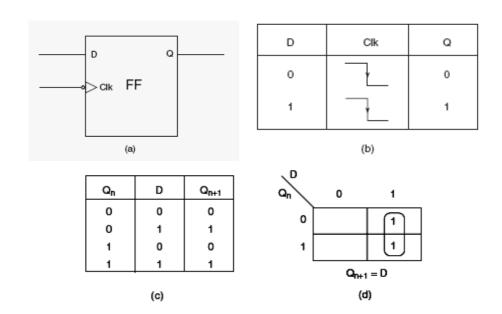

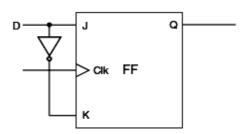

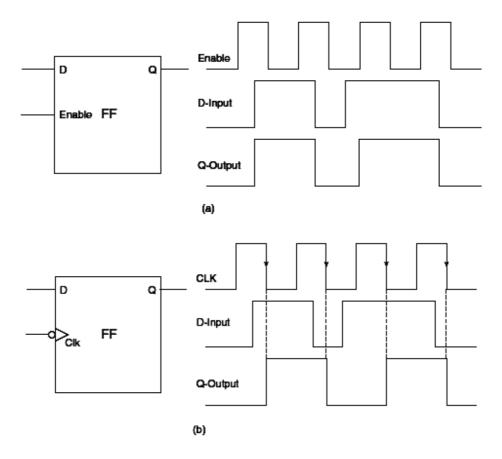

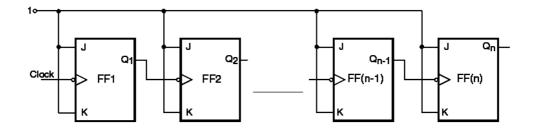

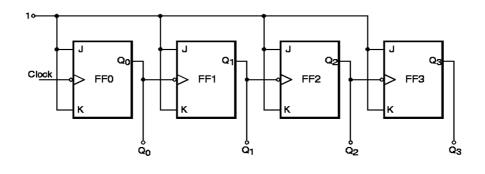

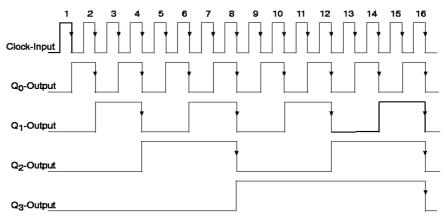

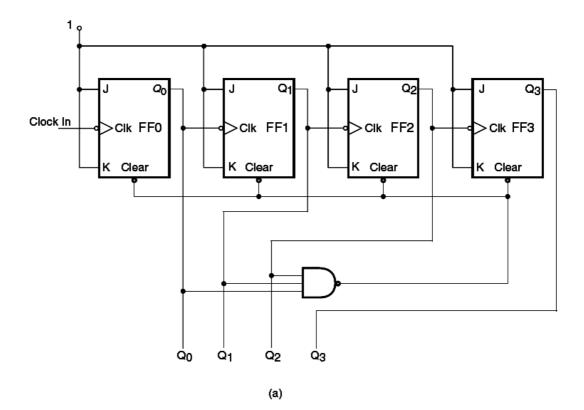

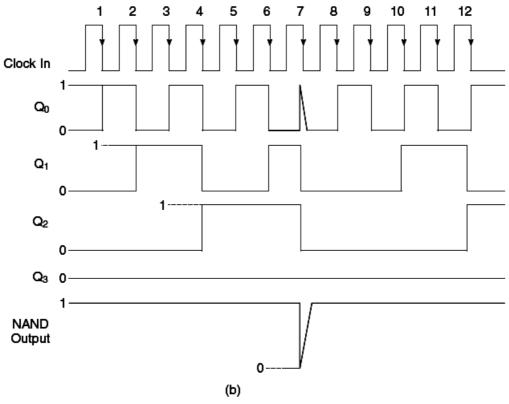

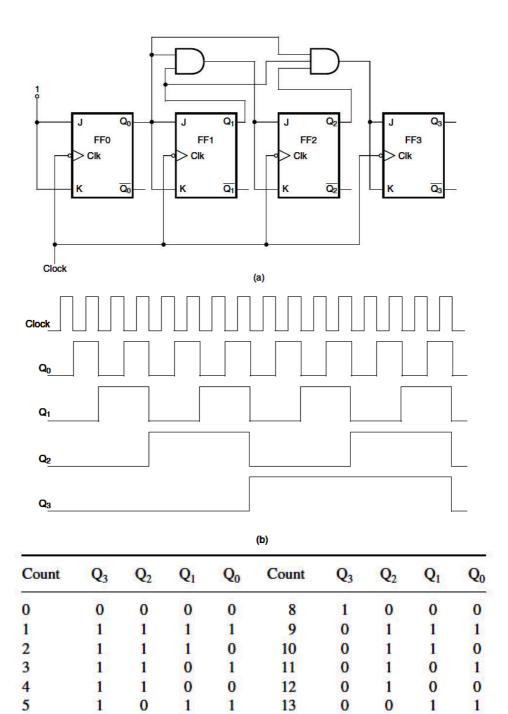

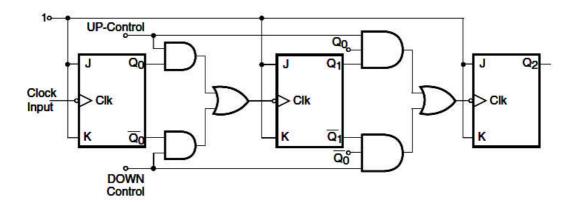

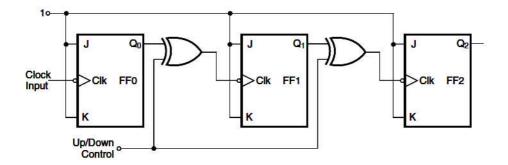

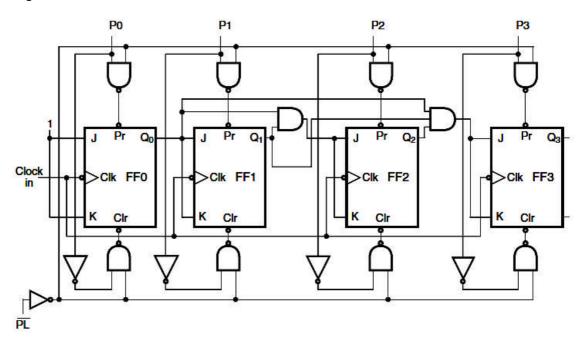

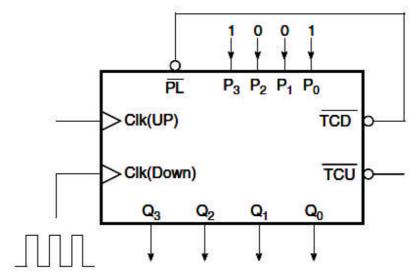

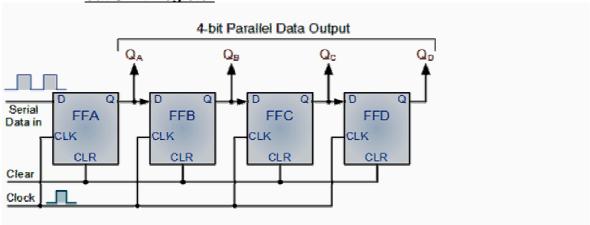

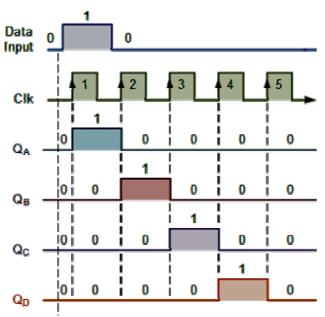

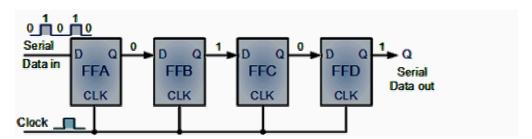

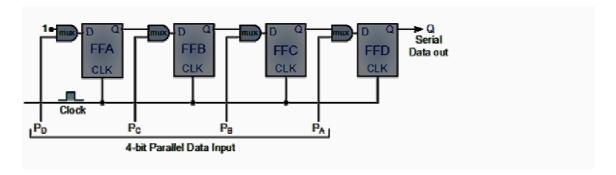

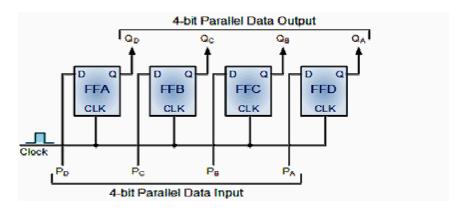

| Unit - IV | Sequential Circuit Design: Flip flops (RS, Clocked RS, D, JK, JK Master Slave, T, Counters, Shift registers and their types, Counters: Synchronous and Asynchronous counters.                                                                                                                                                                                                                                                  |

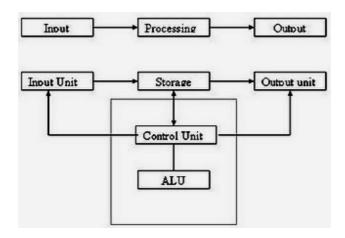

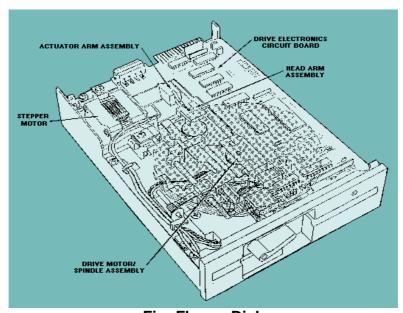

| Unit- V   | Computers:  Basic Organisation, Memory: ROM, RAM, PROM, EPROM, EEPROM, Secondary Memory: Hard Disk and optical Disk, Cache Memory, I/O devices                                                                                                                                                                                                                                                                                 |

| Unit -VI  | Operating Systems:  Types (real Time, Single User / Single Tasking, Single user / Multi tasking, Multi user / Multi tasking, GUI based OS. Overview of desktop operating systems-Windows and LINUX.                                                                                                                                                                                                                            |

#### **Text Books:**

- Modern Digital Electronics by R. P. Jain, 3<sup>rd</sup> Edition, McGraw Hill

- Digital Design and Computer Organisation by Dr. N. S. Gill and J. B. Dixit, University Science Press

- Linux Commands by Bryan Pfaffaenberger BPB Publications

- UNIX by Sumitabha Das, TMH

- References:

- Digital Principles and Applications by Malvino and Leach, McGrawHill

- Introduction to Computers by Peter Norton, McGraw Hill

- Introduction to Computers by Balagurusamy

# DATA AND INFORMATION

#### **Unit Structure**

- 1.0 Objectives

- 1.1 Data & Information

- 1.2 Analog Versus Digital

- 1.3 Number Systems

- 1.4 Decimal Verses Binary Number System

- 1.5 Octal & Hexadecimal Number System

- 1.6 Conversion from Decimal Number System

- 1.7 Unsigned & Signed Integers

- 1.8 Signed Integers

- 1.91's Complement

- 1.10 2's Complement

- 1.11 Binary Arithmetic

- 1.11.1 Addition

- 1.11.2 Subtraction

- 1.11.3 Multiplication

- 1.11.4 Division

- 1.11.5 Binary Subtraction Using 1's Complement

- 1.11.6 Binary Subtraction Using 2's Complement

- 1.12 Questions

- 1.13 Further Reading

#### 1.0 OBJECTIVES

After completing this chapter, you will be able to:

- Understand the concept of Data and Information.

- Differentiate between the Analog Verses digital Signals.

- ❖ Deal with the different number system in arithmetic.

- Understand the number system conversions.

- Solve the Arithmetic examples based on Binary arithmetic.

#### 1.1 DATA AND INFORMATION

Data is raw collection of samples. When this raw data is processed it becomes information. Hence information is processed data. Information is processed data.

#### 1.2 ANALOG VERSUS DIGITAL

| Analog Systems                                                                                                                        | Digital Systems                                                                                             |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| voltage 1                                                                                                                             | voltage 0 1 0 1 1 time                                                                                      |  |  |  |  |

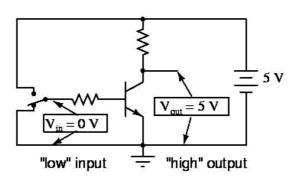

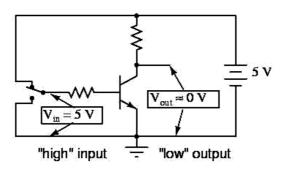

| Continuous time-varying voltages and/or Currents                                                                                      | Discrete signals sampled in time                                                                            |  |  |  |  |

| All possible values are present.                                                                                                      | <ul> <li>Two possible values</li> <li>0V, low, false (logic 0)</li> <li>5V, high, true (logic 1)</li> </ul> |  |  |  |  |

| <ul> <li>Basic elements of analog circuits:</li> <li>Resistors</li> <li>Capacitors</li> <li>Inductors</li> <li>Transistors</li> </ul> | <ul> <li>Basic elements of digital circuits:</li> <li>Logic gates: AND, OR, NOT</li> </ul>                  |  |  |  |  |

#### Advantages of Digital Systems

- Reproducible results

- Relative ease of design

- Flexibility and functionality

- High speed

- Small size

- Low cost

- Low power

- Steadily advancing technology

- Programmable logic devices

Digital techniques and systems have the advantages of being relatively much easier to design and having higher accuracy, programmability, noise immunity, easier storage of data and ease of fabrication in integrated circuit form, leading to availability of more complex functions in a smaller size. The real world, however, is analogue. Most physical quantities — position, velocity, acceleration, force, pressure, temperature and flowrate, for

example – are analogue in nature. That is why analog variables representing these quantities need to be digitized or discretized at the input if we want to benefit from the features and facilities that come with the use of digital techniques. In a typical system dealing with analog inputs and outputs, analog variables are digitized at the input with the help of an analog-to-digital converter block and reconverted back to analogue form at the output using a digital-to-analog converter block.

#### 1.3 NUMBER SYSTEMS

The expression of numerical quantities is something we tend to take for granted. This is both a good and a bad thing in the study of electronics. It is good, in that we are accustomed to the use and manipulation of numbers for the many calculations used in analyzing electronic circuits. On the other hand, the particular system of notation we have been taught from primary school onwards is *not* the system used internally in modern electronic computing devices and learning any different system of notation requires some re-examination of deeply ingrained assumptions. First, we have to distinguish the difference between numbers and the symbols we use to represent numbers. A *number* is a mathematical quantity, usually correlated in electronics to a physical quantity such as voltage, current, or resistance. There are many different types of numbers. Here are just a few types, for example:

WHOLE NUMBERS: 1, 2, 3, 4, 5, 6, 7, 8, 9 . . .

**INTEGERS:**

-4, -3, -2, -1, 0, 1, 2, 3, 4 . . .

**IRRATIONAL NUMBERS:**

$\pi$  (approx. 3.1415927), *e* (approx. 2.718281828), square root of any prime

#### **REAL NUMBERS:**

(All one-dimensional numerical values, negative and positive, including zero, whole, integer, and irrational numbers)

COMPLEX NUMBERS:3 - j4, 34.5 ∠20°

Different types of numbers find different application in the physical world. Whole numbers work well for counting discrete objects, such as the number of resistors in a circuit. Integers are needed when negative equivalents of whole numbers are required.

Irrational numbers are numbers that cannot be exactly expressed as the ratio of two integers, and the ratio of a perfect circle's circumference to its diameter  $(\pi)$  is a good physical example of this. The non-integer quantities of voltage, current, and resistance that we're used to dealing with in DC circuits can be expressed as real numbers, in either fractional or decimal form. For AC circuit analysis, however, real numbers fail to capture the dual essence of magnitude and phase angle, and so we turn to the use of complex numbers in either rectangular or polar form.

If we are to use numbers to understand processes in the physical world, make scientific predictions, or balance our checkbooks, we must have a way of symbolically denoting them. In other words, we may know how much money we have in our checking account, but to keep record of it we need to have some system worked out to symbolize that quantity on paper, or in some other kind of form for record-keeping and tracking. There are two basic ways we can do this: analog and digital. With analog representation, the quantity is symbolized in a way that is infinitely divisible. With digital representation, the quantity is symbolized in a way that is discretely packaged.

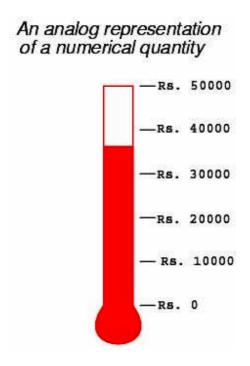

We are familiar with an analog representation of money, and didn't realize it for what it was. Have you ever seen a fund-raising poster made with a picture of a thermometer on it, where the height of the red column indicated the amount of money collected for the cause? The more money collected, the taller the column of red ink on the poster.

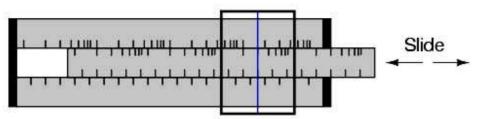

This is an example of an analog representation of a number. There is no real limit to how finely divided the height of that column can be made to symbolize the amount of money in the account. Changing the height of that column is something that can be done without changing the essential nature of what it is. Length is a physical quantity that can be divided as small as you would like, with no practical limit. The slide rule is a mechanical device that uses the very same physical quantity -- length -- to represent numbers, and to help perform arithmetical operations with two or more numbers at a time. It, too, is an analog device.

On the other hand, a *digital* representation of that same monetary figure, written with standard symbols (sometimes called ciphers), looks like this: Rs. 35,955.38

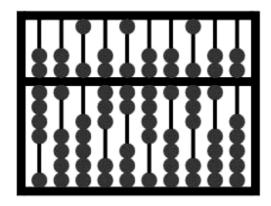

Unlike the "thermometer" poster with its red column, those symbolic characters above cannot be finely divided: that particular combination of ciphers stand for one quantity and one quantity only. If more money is added to the account (+ \$40.12), different symbols must be used to represent the new balance (\$35,995.50), or at least the same symbols arranged in different patterns. This is an example of digital representation. The counterpart to the slide rule (analog) is also a digital device: the abacus, with beads that are moved back and forth on rods to symbolize numerical quantities:

# Slide rule (an analog device)

Numerical quantities are represented by the positioning of the slide.

### Abacus (a digital device)

Numerical quantities are represented by the discrete positions of the beads.

Lets contrast these two methods of numerical representation: ANALOG DIGITAL

-----

Intuitively understood ----- Requires training to interpret Infinitely divisible ----- Discrete

Prone to errors of precision ----- Absolute precision

Interpretation of numerical symbols is something we tend to take for granted, because it has been taught to us for many years. However, if you were to try to communicate a quantity of something to a person ignorant of decimal numerals, that person could still understand the simple thermometer chart!

The infinitely divisible vs. discrete and precision comparisons are really flip-sides of the same coin. The fact that digital representation is composed of individual, discrete symbols (decimal digits and abacus beads) necessarily means that it will be able to symbolize quantities in precise steps. On the other hand, an analog representation (such as a slide rule's length) is not composed of individual steps, but rather a continuous range of motion. The ability for a slide rule to characterize a numerical quantity to infinite resolution is a trade-off for imprecision. If a slide rule is bumped, an error will be introduced into the representation of the number that was "entered" into it. However, an abacus must be bumped much harder before its beads are completely dislodged from their places (sufficient to represent a different number).

Please don't misunderstand this difference in precision by thinking that digital representation is necessarily more accurate than analog. Just because a clock is digital doesn't mean that it will always read time more accurately than an analog clock, it just means that the *interpretation* of its display is less ambiguous.

Divisibility of analog versus digital representation can be further illuminated by talking about the representation of irrational numbers. Numbers such as  $\pi$  are called irrational, because they cannot be exactly expressed as the fraction of integers, or whole numbers. Although you might have learned in the past that the fraction 22/7 can be used for  $\pi$  in calculations, this is just an approximation. The actual number "pi" cannot be exactly expressed by any finite, or limited, number of decimal places. The digits of  $\pi$  go on forever:

3.1415926535897932384 . . . . .

It is possible, at least theoretically, to set a slide rule (or even a thermometer column) so as to perfectly represent the number  $\pi$ , because analog symbols have no minimum limit to the degree that they can be increased or decreased. If my slide rule shows a figure of 3.141593 instead of 3.141592654, I can bump the slide just a bit more (or less) to get it closer yet. However, with digital representation, such as with an abacus, I would need additional rods (place holders, or digits) to represent  $\pi$  to further degrees of precision. An abacus with 10 rods simply cannot represent any more than 10 digits worth of the number  $\pi$ , no matter how I set the beads. To perfectly represent  $\pi$ , an abacus would have to have an infinite number of beads and rods! The tradeoff, of course, is the practical limitation to adjusting, and reading, analog symbols. Practically speaking, one cannot read a slide rule's scale to the 10th digit of precision, because the marks on the scale are too coarse and human vision is too limited. An abacus, on the other hand, can be set and read with no interpretational errors at all.

Furthermore, analog symbols require some kind of standard by which they can be compared for precise interpretation. Slide rules have markings printed along the length of the slides to translate length into standard quantities. Even the thermometer chart has numerals written along its height to show how much money (in Rupees) the red column represents for any given amount of height. Imagine if we all tried to communicate simple numbers to each other by spacing our hands apart varying distances. The number 1 might be signified by holding our hands 1 inch apart, the number 2 with 2 inches, and so on. If someone held their hands 17 inches apart to represent the number 17, would everyone around them be able to immediately and accurately interpret that distance as 17? Probably not. Some would guess short (15 or 16) and some would guess long (18 or 19). Of course, fishermen who brag about their catches don't mind overestimations in quantity!

Perhaps this is why people have generally settled upon digital symbols for representing numbers, especially whole numbers and integers, which find the most application in everyday life. Using the fingers on our hands, we have a ready means of

symbolizing integers from 0 to 10. We can make tally marks on paper, wood, or stone to represent the same quantities quite easily:

For large numbers, though, the "tally mark" number system is too inefficient.

# 1.4 DECIMAL VERSUS BINARY NUMBER SYSTEMS

Let's count from zero to twenty using four different kinds of number systems: Roman numerals, decimal and binary:

| Decimal | Roman | Binary | Octal | Hexadecimal |

|---------|-------|--------|-------|-------------|

| 0       | -     | 0      | 0     | 0           |

| 1       | I     | 1      | 1     | 1           |

| 2       | II    | 01     | 2     | 2           |

| 3       | III   | 11     | 3     | 3           |

| 4       | IV    | 100    | 4     | 4           |

| 5       | V     | 101    | 5     | 5           |

| 6       | VI    | 110    | 6     | 6           |

| 7       | VII   | 111    | 7     | 7           |

| 8       | VIII  | 1000   | 10    | 8           |

| 9       | IX    | 1001   | 11    | 9           |

| 10      | X     | 1010   | 12    | А           |

| 11      | ΧI    | 1011   | 13    | В           |

| 12      | XII   | 1100   | 14    | С           |

| 13      | XIII  | 1101   | 15    | D           |

| 14      | XIV   | 1110   | 16    | E           |

| 15      | XV    | 1110   | 17    | F           |

The Roman system is not very practical for symbolizing large numbers. Obviously, place-weighted systems such as decimal and binary are more efficient for the task. Notice, though, how much shorter decimal notation is over binary notation, for the same number of quantities. What takes five bits in binary notation only takes two digits in decimal notation.

This raises an interesting question regarding different number systems: how large of a number can be represented with a limited number of cipher positions, or places? With the crude hashmark system, the number of places IS the largest number that can be represented, since one hash mark "place" is required for every integer step. For place-weighted systems of numeration, however, the answer is found by taking base of the number system (10 for decimal, 2 for binary) and raising it to the power of the number of places. For example, 5 digits in a decimal numeration system can represent 100,000 different integer number values, from 0 to 99,999 (10 to the 5th power = 100,000). 8 bits in a binary numeration system can represent 256 different integer number values, from 0 to 11111111 (binary), or 0 to 255 (decimal), because 2 to the 8th power equals 256. With each additional place position to the number field, the capacity for representing numbers increases by a factor of the base (10 for decimal, 2 for binary).

An interesting footnote for this topic is the one of the first electronic digital computers, the Eniac. The designers of the Eniac chose to represent numbers in decimal form, digitally, using a series of circuits called "ring counters" instead of just going with the binary numeration system, in an effort to minimize the number of circuits required to represent and calculate very large numbers. This approach turned out to be counter-productive, and virtually all digital computers since then have been purely binary in design.

To convert a number in binary numeration to its equivalent in decimal form, all you have to do is calculate the sum of all the products of bits with their respective place-weight constants. To illustrate:

Convert 11001101<sub>2</sub> to decimal form:

The bit on the far right side is called the Least Significant Bit (LSB), because it stands in the place of the lowest weight (the one's place). The bit on the far left side is called the Most Significant Bit (MSB), because it stands in the place of the highest weight (the one hundred twenty-eight's place). Remember, a bit value of "1" means that the respective place weight gets added to the total value, and a bit value of "0" means that the respective place weight does *not* get added to the total value. With the above example, we have:

$128_{10} + 64_{10} + 8_{10} + 4_{10} + 1_{10} = 205_{10}$

If we encounter a binary number with a dot (.), called a "binary point" instead of a decimal point, we follow the same procedure, realizing that each place weight to the right of the point is one-half the value of the one to the left of it (just as each place weight to the right of a *decimal* point is one-tenth the weight of the one to the left of it).

#### For example:

Convert 101.011<sub>2</sub> to decimal form:

# 1.5 OCTAL AND HEXADECIMAL NUMBER SYSTEMS:

Because binary number system requires so many bits to represent relatively small numbers compared to the economy of the decimal system, analyzing the numerical states inside of digital electronic circuitry can be a tedious task. Computer programmers who design sequences of number codes instructing a computer what to do would have a very difficult task if they were forced to work with nothing but long strings of 1's and 0's, the "native language" of any digital circuit. To make it easier for human engineers, technicians, and programmers to "speak" this language of the digital world, other systems of place-weighted number system have been made which are very easy to convert to and from binary.

One of those number systems is called *octal*, because it is a place-weighted system with a base of eight. Valid ciphers include the symbols 0, 1, 2, 3, 4, 5, 6, and 7. Each place weight differs from the one next to it by a factor of eight.

Another system is called *hexadecimal*, because it is a place-weighted system with a base of sixteen. Valid ciphers include the normal decimal symbols 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9, plus six alphabetical characters A, B, C, D, E, and F, to make a total of sixteen. As you might have guessed already, each place weight differs from the one before it by a factor of sixteen.

Let's count again from zero to twenty using decimal, binary, octal, and hexadecimal to contrast these systems of numbers:

| Number    | Decimal | Binary | Octal | Hexadecimal |

|-----------|---------|--------|-------|-------------|

|           |         |        |       |             |

| Zero      | 0       | 0      | 0     | 0           |

| One       | 1       | 1      | 1     | 1           |

| Two       | 2       | 10     | 2     | 2           |

| Three     | 3       | 11     | 3     | 3           |

| Four      | 4       | 100    | 4     | 4           |

| Five      | 5       | 101    | 5     | 5           |

| Six       | 6       | 110    | 6     | 6           |

| Seven     | 7       | 111    | 7     | 7           |

| Eight     | 8       | 1000   | 10    | 8           |

| Nine      | 9       | 1001   | 11    | 9           |

| Ten       | 10      | 1010   | 12    | Α           |

| Eleven    | 11      | 1011   | 13    | В           |

| Twelve    | 12      | 1100   | 14    | С           |

| Thirteen  | 13      | 1101   | 15    | D           |

| Fourteen  | 14      | 1110   | 16    | E           |

| Fifteen   | 15      | 1111   | 17    | F           |

| Sixteen   | 16      | 10000  | 20    | 10          |

| Seventeen | 17      | 10001  | 21    | 11          |

| Eighteen  | 18      | 10010  | 22    | 12          |

| Nineteen  | 19      | 10011  | 23    | 13          |

| Twenty    | 20      | 10100  | 24    | 14          |

Octal and hexadecimal number systems would be pointless if not for their ability to be easily converted to and from binary notation. Their primary purpose in being is to serve as a "shorthand" method of denoting a number represented electronically in binary form. Because the bases of octal (eight) and hexadecimal (sixteen) are even multiples of binary's base (two), binary bits can be grouped together and directly converted to or from their respective octal or hexadecimal digits. With octal, the binary bits are grouped in three's (because  $2^3 = 8$ ), and with hexadecimal, the binary bits grouped in are (because  $2^4 = 16$ ):

# BINARY TO OCTAL CONVERSION Convert 10110111.1<sub>2</sub> to octal:

|                          | impl | ied ze | implied zeros |     |

|--------------------------|------|--------|---------------|-----|

|                          |      |        |               |     |

|                          | 010  | 110    | 111           | 100 |

| Convert each group of b  | its  |        |               |     |

| to its octal equivalent: | 2    | 6      | 7             | 4   |

**Answer:**  $10110111.1_2 = 267.4_8$

We had to group the bits in three's, from the binary point left, and from the binary point right, adding (implied) zeros as necessary to make complete 3-bit groups. Each octal digit was translated from the 3-bit binary groups. Binary-to-Hexadecimal conversion is much the same:

BINARY TO HEXADECIMAL CONVERSION Convert 10110111.1<sub>2</sub> to hexadecimal:

.

implied zeros

1011 0111 1000

Convert each group of bits ---- to its hexadecimal equivalent: B 7 8

.

**Answer:**  $10110111.1_2 = B7.8_{16}$

Here we had to group the bits in four's, from the binary point left, and from the binary point right, adding (implied) zeros as necessary to make complete 4-bit groups:

Likewise, the conversion from either octal or hexadecimal to binary is done by taking each octal or hexadecimal digit and converting it to its equivalent binary (3 or 4 bit) group, then putting all the binary bit groups together.

Incidentally, hexadecimal notation is more popular, because binary bit groupings in digital equipment are commonly multiples of eight (8, 16, 32, 64, and 128 bit), which are also multiples of 4. Octal, being based on binary bit groups of 3, doesn't work out evenly with those common bit group sizings.

# 1.6 CONVERSION FROM DECIMAL NUMBER SYSTEM

Because octal and hexadecimal number systems have bases that are multiples of binary (base 2), conversion back and forth between either hexadecimal or octal and binary is very easy. Also, because we are so familiar with the decimal system, converting binary, octal, or hexadecimal to decimal form is relatively easy (simply add up the products of cipher values and placeweights). However, conversion from decimal to any of these "strange" number systems is a different matter.

The method which will probably make the most sense is the "trial-and-fit" method, where you try to "fit" the binary, octal, or hexadecimal notation to the desired value as represented in decimal form. For example, let's say that I wanted to represent the decimal value of 87 in binary form. Let's start by drawing a binary number field, complete with place-weight values:

.

```

weight = 1 6 3 1 8 4 2 1 (in decimal 2 4 2 6 notation) 8

```

Well, we know that we won't have a "1" bit in the 128's place, because that would immediately give us a value greater than 87. However, since the next weight to the right (64) is less than 87, we know that we must have a "1" there.

```

. 1

. - - - - - Decimal value so far = 64<sub>10</sub>

weight = 6 3 1 8 4 2 1

(in decimal 4 2 6

notation)

```

If we were to make the next place to the right a "1" as well, our total value would be  $64_{10} + 32_{10}$ , or  $96_{10}$ . This is greater than  $87_{10}$ , so we know that this bit must be a "0". If we make the next (16's) place bit equal to "1," this brings our total value to  $64_{10} + 16_{10}$ , or  $80_{10}$ , which is closer to our desired value ( $87_{10}$ ) without exceeding it:

```

. 1 0 1

. - - - - - Decimal value so far = 80<sub>10</sub>

weight = 6 3 1 8 4 2 1

(in decimal 4 2 6

notation)

```

By continuing in this progression, setting each lesser-weight bit as we need to come up to our desired total value without exceeding it, we will eventually arrive at the correct figure:

```

. 1 0 1 0 1 1 1

. - - - - - Decimal value so far = 87<sub>10</sub>

weight = 6 3 1 8 4 2 1

(in decimal 4 2 6

notation)

```

This trial-and-fit strategy will work with octal and hexadecimal conversions, too. Let's take the same decimal figure,  $87_{10}$ , and convert it to octal number system:

```

weight = 6 8 1 (in decimal 4 notation)

```

If we put a cipher of "1" in the 64's place, we would have a total value of  $64_{10}$  (less than  $87_{10}$ ). If we put a cipher of "2" in the 64's place, we would have a total value of  $128_{10}$  (greater than  $87_{10}$ ). This tells us that our octal number system must start with a "1" in the 64's place:

```

. 1

. weight = - - - Decimal value so far = 64_{10}

681

(in decimal 4 notation)

```

Now, we need to experiment with cipher values in the 8's place to try and get a total (decimal) value as close to 87 as possible without exceeding it. Trying the first few cipher options, we get:

```

"1" = 64_{10} + 8_{10} = 72_{10}

"2" = 64_{10} + 16_{10} = 80_{10}

"3" = 64_{10} + 24_{10} = 88_{10}

```

A cipher value of "3" in the 8's place would put us over the desired total of  $87_{10}$ , so "2" it is!

```

. 1 2 . . - - Decimal value so far = 80_{10} weight = 6 8 1 (in decimal 4 notation)

```

Now, all we need to make a total of 87 is a cipher of "7" in the 1's place:

```

. 1 2 7

. - - Decimal value so far = 87<sub>10</sub>

weight = 6 8 1

(in decimal 4

notation)

```

Of course, if you were paying attention during the last section on octal/binary conversions, you will realize that we can take the binary representation of (decimal)  $87_{10}$ , which we previously determined to be  $1010111_2$ , and easily convert from that to octal to check our work:

```

. Implied zeros

. ||

. 001 010 111 Binary

. --- ---

. 1 2 7 Octal

```

Answer:  $1010111_2 = 127_8$

Can we do decimal-to-hexadecimal conversion the same way? Sure, but who would want to? This method is simple to understand, but laborious to carry out. There is another way to do these conversions, which is essentially the same (mathematically), but easier to accomplish.

This other method uses repeated cycles of division (using decimal notation) to break the decimal number system down into multiples of binary, octal, or hexadecimal place-weight values. In the first cycle of division, we take the original decimal number and divide it by the base of the number system that we're converting to (binary=2 octal=8, hex=16). Then, we take the whole-number portion of division result (quotient) and divide it by the base value again, and so on, until we end up with a quotient of less than 1. The binary, octal, or hexadecimal digits are determined by the "remainders" left over by each division step. Let's see how this works for binary, with the decimal example of 87<sub>10</sub>:

```

. 87

Divide 87 by 2, to get a quotient of 43.5

. --- = 43.5

Division "remainder" = 1, or the < 1 portion

of the quotient times the divisor (0.5 \times 2)

2

43

Take the whole-number portion of 43.5 (43)

. --- = 21.5

and divide it by 2 to get 21.5, or 21 with

a remainder of 1

21

And so on . . . remainder = 1 (0.5 \times 2)

--- = 10.5

2

10

And so on . . . remainder = 0

---=5.0

2

5

And so on . . . remainder = 1 (0.5 \times 2)

. --- = 2.5

2

2

And so on . . . remainder = 0

. --- = 1.0

. 2

. . . until we get a quotient of less than 1

. --- = 0.5

remainder = 1 (0.5 \times 2)

2

```

The binary bits are assembled from the remainders of the successive division steps, beginning with the LSB and proceeding to the MSB. In this case, we arrive at a binary notation of 1010111<sub>2</sub>.

When we divide by 2, we will always get a quotient ending with either ".0" or ".5", i.e. a remainder of either 0 or 1. As was said before, this repeat-division technique for conversion will work for number systems other than binary. If we were to perform successive divisions using a different number, such as 8 for conversion to octal, we will necessarily get remainders between 0 and 7. Let's try this with the same decimal number, 87<sub>10</sub>:

```

. 87 Divide 87 by 8, to get a quotient of 10.875

. --- = 10.875 Division "remainder" = 7, or the < 1 portion</li>

. 8 of the quotient times the divisor (.875 x 8)

. 10

. --- = 1.25 Remainder = 2

. 8

. 1

. --- = 0.125 Quotient is less than 1, so we'll stop here.

. 8 Remainder = 1

. RESULT: 87<sub>10</sub> = 127<sub>8</sub>

```

We can use a similar technique for converting number systems dealing with quantities less than 1, as well. For converting a decimal number less than 1 into binary, octal, or hexadecimal, we use repeated multiplication, taking the integer portion of the product in each step as the next digit of our converted number. Let's use the decimal number 0.8125<sub>10</sub> as an example, converting to binary:

```

0.8125 x 2 = 1.625 Integer portion of product = 1

0.625 x 2 = 1.25 Take < 1 portion of product and remultiply Integer portion of product = 1</li>

0.25 x 2 = 0.5 Integer portion of product = 0

0.5 x 2 = 1.0 Integer portion of product = 1

Stop when product is a pure integer (ends with .0)

RESULT: 0.8125<sub>10</sub> = 0.1101<sub>2</sub>

```

As with the repeat-division process for integers, each step gives us the next digit (or bit) further away from the "point." With integer (division), we worked from the LSB to the MSB (right-to-left), but with repeated multiplication, we worked from the left to the right. To convert a decimal number greater than 1, with a < 1

component, we must use *both* techniques, one at a time. Take the decimal example of 54.40625<sub>10</sub>, converting to binary:

#### REPEATED DIVISION FOR THE INTEGER PORTION:

```

54

--- = 27.0

Remainder = 0

27

--- = 13.5

Remainder = 1 (0.5 \times 2)

2

13

--- = 6.5

Remainder = 1(0.5 \times 2)

2

--- = 3.0

Remainder = 0

2

3

--- = 1.5

Remainder = 1(0.5 \times 2)

2

--- = 0.5

Remainder = 1 (0.5 \times 2)

PARTIAL ANSWER: 54_{10} = 110110_2

REPEATED MULTIPLICATION FOR THE < 1 PORTION:

0.40625 \times 2 = 0.8125 Integer portion of product = 0

. 0.8125 \times 2 = 1.625 Integer portion of product = 1

Integer portion of product = 1

0.625 \times 2 = 1.25

Integer portion of product = 0

0.25 \times 2 = 0.5

0.5 \times 2 = 1.0

Integer portion of product = 1

. PARTIAL ANSWER: 0.40625_{10} = 0.01101_2

. COMPLETE ANSWER: 54_{10} + 0.40625_{10} = 54.40625_{10}

110110_2 + 0.01101_2 = 110110.01101_2

```

#### 1.7 UNSIGNED AND SIGNED INTEGERS

An integer is a number with no fractional part; it can be positive, negative or zero. In ordinary usage, one uses a minus sign

to designate a negative integer. However, a computer can only store information in bits, which can only have the values zero or one. We might expect, therefore, that the storage of negative integers in a computer might require some special technique. It is for that reason that we began this section with a discussion of unsigned integers.

As you might imagine, an **unsigned integer** is either positive or zero. Consider a single digit decimal number: in a single decimal digit, you can write a number between 0 and 9. In two decimal digits, you can write a number between 0 and 99, and so on. Since nine is equivalent to  $10^{1}$  - 1, 99 is equivalent to  $10^{2}$  - 1, etc., in n decimal digits, you can write a number between 0 and  $10^{n}$  - 1. Analogously, in the binary number system, an **unsigned integer containing n bits can have a value between 0 and 2^{n} - 1 (which is 2^{n} different values).**

This fact is one of the most important and useful things to know about computers. When a computer program is written, the programmer, either explicitly or implicitly, must decide how many bits are used to store any given quantity. Once the decision is made to use n bits to store it, the program has an inherent limitation: that quantity can only have a value between 0 and 2  $^{\rm n}$  - 1. You will meet these limitations in one form or another in every piece of hardware and software that you will learn about during your career:

- the BIOS (Basic Input Output Software) in older PCs uses 10 bits to store the cylinder number on the hard drive where your operating system begins; therefore those PCs cannot boot an operating system from a cylinder greater than 2 <sup>10</sup> 1, or 1023.

- a FAT12 file system (used on Windows diskettes), which allocates file space in units called "clusters", uses 12 bits to store cluster numbers; therefore there can be no more than 2  $^{12}$  1 or 4,095 clusters in such a file system.

- a UNIX system keeps track of the processes (programs) it runs using a PID (Process IDentifier); for typical memory sizes, the PID is 16 bits long and so after 2 <sup>16</sup> 1 or 65,535 processes, the PIDs must start over at the lowest number not currently in use.

- These are just a few examples of this basic principle.

Most modern computers store memory in units of 8 bits, called a "byte" (also called an "octet"). Arithmetic in such computers can be done in bytes, but is more often done in larger units called "(short) integers" (16 bits), "long integers" (32 bits) or "double integers" (64 bits). Short integers can be used to store numbers between 0 and 2 <sup>16</sup> 1, or 65,535. Long integers can be used to store numbers

between 0 and 2  $^{32}$  - 1, or 4,294,967,295. and double integers can be used to store numbers between 0 and 2  $^{64}$  - 1, or 18,446,744,073,709,551,615. (Check these!)

When a computer performs an unsigned integer arithmetic operation, there are three possible problems which can occur:

- 1. if the result is too large to fit into the number of bits assigned to it, an "**overflow**" is said to have occurred. For example if the result of an operation using 16 bit integers is larger than 65,535, an overflow results.

- 2. in the division of two integers, if the result is not itself an integer, a "**truncation**" is said to have occurred: 10 divided by 3 is truncated to 3, and the extra 1/3 is lost. This is not a problem, of course, if the programmer's intention was to ignore the remainder!

- 3. any division by zero is an error, since division by zero is not possible in the context of arithmetic.

#### 1.8 SIGNED INTEGERS

**Signed integers** are stored in a computer using 2's complement. As you recall, when computing the 2's complement of a number it was necessary to know how many bits were to be used in the final result; leading zeroes were appended to the most significant digit in order to make the number the appropriate length. Since the process of computing the 2's complement involves first computing the 1's complement, these leading zeros become leading ones, and the left most bit of a negative number is therefore always 1. In computers, the left most bit of a signed integer is called the "**sign bit**".

Consider an 8 bit signed integer: let us begin with 0 0 0 0 0 0 0  $_2$  and start counting by repeatedly adding 1:

- When you get to 127, the integer has a value of 0 1 1 1 1 1 1 1  $_2$ ; this is easy to see because you know now that a 7 bit integer can contain a value between 0 and 2  $^7$  1, or 127. What happens when we add 1?

- If the integer were unsigned, the next value would be 1 0 0 0 0 0 0  $_2$ , or 128 (2  $^7$ ). But since this is a signed integer, 1 0 0 0 0 0 0 0  $_2$  is a negative value: the sign bit is 1!

- Since this is the case, we must ask the question: what is the decimal value corresponding to the signed integer 1 0 0 0 0 0 0 0 2? To answer this question, we must take the 2's

complement of that value, by first taking the 1's complement and then adding one.

- The 1's complement is 0 1 1 1 1 1 1 1  $_2$ , or decimal 127. Since we must now add 1 to that, our conclusion is that the signed integer 1 0 0 0 0 0 0  $_2$  must be equivalent to decimal -128! Odd as this may seem, it is in fact the only consistent way to interpret 2's complement signed integers. Let us continue now to "count" by adding 1 to 1 0 0 0 0 0 0  $_2$ :

- $10000000_2 + 00000001_2$  is  $10000001_2$ .

- To find the decimal equivalent of 1 0 0 0 0 0 0 1  $_2$ , we again take the 2's complement: the 1's complement is 0 1 1 1 1 1 1 0  $_2$  and adding 1 we get 0 1 1 1 1 1 1 1  $_2$  (127) so 1 0 0 0 0 0 0 1  $_2$  is equivalent to -127.

- We see then that once we have accepted the fact that 1 0 0 0 0 0 0  $_2$  is decimal -128, counting by adding one works as we would expect.

- Note that the most negative number which we can store in an 8 bit signed integer is -128, which is  $2^{8-1}$ , and that the largest positive signed integer we can store in an 8 bit signed integer is 127, which is  $2^{8-1}$  1.

- The number of integers between -128 and + 127 (inclusive) is 256, which is 2 <sup>8</sup>; this is the same number of values which an unsigned 8 bit integer can contain (from 0 to 255).

- Eventually we will count all the way up to 1 1 1 1 1 1 1 1 2. The 1's complement of this number is obviously 0, so 1 1 1 1 1 1 1 1 2 must be the decimal equivalent of -1. Using our deliberations on 8 bit signed integers as a guide, we come to the following observations about signed integer arithmetic in general:

- if a signed integer has n bits, it can contain a number between  $2^{n-1}$  and +  $(2^{n-1} 1)$ .

- since both signed and unsigned integers of n bits in length can represent 2 n different values, there is no inherent way to distinguish signed integers from unsigned integers simply by looking at them; the software designer is responsible for using them correctly.

- no matter what the length, if a signed integer has a binary value of all 1's, it is equal to decimal -1.

You should verify that a signed short integer can hold decimal values from -32,768 to +32,767, a signed long integer can contain values from -2,147,483,648 to +2,147,483,647 and a signed double integer can represent decimal values from -9,223, 372, 036, 854, 775, 808 to +9,223, 372, 036, 854, 775, 807.

There is an interesting consequence to the fact that in 2's complement arithmetic, one expects to throw away the final carry: in unsigned arithmetic a carry out of the most significant digit means that there has been an overflow, but in signed arithmetic an overflow is not so easy to detect. In fact, signed arithmetic overflows are detected by checking the consistency of the signs of the operands and the final answer. A signed overflow has occurred in an addition or subtraction if:

- the sum of two positive numbers is negative;

- the sum of two negative numbers is non-negative;

- subtracting a positive number from a negative one yields a positive result; or

- subtracting a negative number from a non-negative one yields a negative result.

Integer arithmetic on computers is often called "**fixed point**" arithmetic and the integers themselves are often called fixed point numbers. Real numbers on computers (which may have fractional parts) are often called "floating point" numbers.

#### 1.9 1'S COMPLEMENT

Binary numbers can also be represented by 'radix' and 'radix -1' forms. 1's complement of a binary number N is obtained by the formula  $: -(2^n - 1) - N$  where n is the no of bits in number N

#### Example

Convert binary number 111001101 to 1's complement.

#### Method:

N = 111001101

n = 9

$2^n = 256 = 100000000$

2<sup>n</sup> -1 = 255 = 11111111

1's complement of N = (100000000 - 1) - 111001101

011111111

-111001101

= 000110010

Answer:

1's complement of N is 000110010

#### Trick:

Invert all the bits of the binary number N = 111001101

#### 1.10 2'S COMPLEMENT

2's complement of a binary number N is obtained by the formula  $(2^n) - N$

where n is the no of bits in number N

#### **Example:**

Convert binary number 111001101 to 2's complement

#### **Method**

2's complement of a binary no can be obtained by two step process Step 1

1's complement of number N = 000110010

Step 2

1's complement + 1

000110010

+ 00000001

= 000110011

#### **Answer**

2's complement of a binary no 111001101 is 000110011

<u>Trick</u>: 2's complement can be represented by keeping all lower significant bits till first 1 as it is and taking complement of all upper bits after that.

#### 1.11 BINARY ARITHMETIC

#### 1.11.1 Addition

- 0 + 0 = 0

- 0 + 1 = 1

- 1 + 0 = 1

- 1 + 1 = 0, and carry 1 to the next more significant bit

For example.

#### 1.11.2 Subtraction

- 0 0 = 0

- 0 1 = 1, and borrow 1 from the next more significant bit

- 1 0 = 1

- 1 1 = 0

#### For example,

#### 1.11.3 Multiplication

- $\bullet \qquad 0 \times 0 = 0$

- 0 x 1 = 0

- $1 \times 0 = 0$

- 1 x 1 = 1, and no carry or borrow bits

#### For example,

$00101001 \times 00000110 = 11110110$

$$00010111 \times 00000011 = 01000101$$

$$0 0 0 1 0 1 1 1 = 23_{(base 10)}$$

$$\times 0 0 0 0 0 0 1 1 = 3_{(base 10)}$$

$$0 0 1 0 1 0 1 1 1$$

$$0 0 0 1 0 1 1 1$$

$$0 0 1 0 0 0 1 0 1 = 69_{(base 10)}$$

**Another Method:** Binary multiplication is the same as repeated binary addition; add the multicand to itself the multiplier number of times.

$00001000 \times 00000011 = 00011000$

#### 1.11.4 Division

Binary division is the repeated process of subtraction, just as in decimal division.

#### For example,

$$00101010 \div 00000110 = 00000111$$

#### **Binary Number System**

System Digits: 0 and 1

Bit (short for *b*inary dig*it*): A single binary digit LSB (least significant bit): The rightmost bit MSB (most significant bit): The leftmost bit

Upper Byte (or nibble): The right-hand byte (or nibble) of a pair Lower Byte (or nibble): The left-hand byte (or nibble) of a pair

#### **Binary Equivalents**

- 1 Nibble = 4 bits

- 1 Byte = 2 nibbles = 8 bits

- 1 Kilobyte (KB) = 1024 bytes

- 1 Megabyte (MB) = 1024 kilobytes = 1,048,576 bytes

- 1 Gigabyte (GB) = 1024 megabytes = 1,073,741,824 bytes

#### 1.11.5 Binary subtraction using 1's complement

Let's consider how we would solve our problem of subtracting  $\mathbf{1}_{10}$  from  $\mathbf{7}_{10}$  using 1's complement.

- 1. First, we need to convert 0001<sub>2</sub> to its negative equivalent in 1's complement. 0111 (7) 0001 (1)

- 2. To do this we change all the 1's to 0's and 0's to 1's. Notice that the most-significant digit is now 1 since the number is negative.

0101

0110

(6)

(1)

1111

| 3. Next, we add the negative value we                     | 0111          | (7)          |

|-----------------------------------------------------------|---------------|--------------|

| computed to 0111 <sub>2</sub> . This gives us a result of | <u>+ 1110</u> | <b>+(-1)</b> |

| 10101 <sub>2</sub> .                                      | 10101         | (?)          |

- Notice that our addition caused an overflow bit. Whenever we have an overflow bit in 1's complement, we add this bit to our sum to get the correct answer. If there is no overflow bit, then we leave the sum as it is.

- 0111 (7)This gives us a final answer of 0110<sub>2</sub> 5. - 0001 - (1) (or  $6_{10}$ ). 0110 (6)

Now let's look at an example where our problem does not generate an overflow bit. We will subtract 7<sub>10</sub> from 1<sub>10</sub> using 1's complement.

- 0001 (1) 1. First, we state our problem in binary. <u>- 0111 - (7)</u>

- 0001 (1) 2. Next, we convert 01112 to its negative +1000 + (-7)equivalent and add this to 0001<sub>2</sub>. 1001 (?)

- 3. This time our result does not cause an overflow, so we do not need to adjust the sum. Notice that our final answer is a negative number since it begins with a 1. 0001 Remember that our answer is in 1's + 1000 +(-7) complement notation so the correct decimal 1001 (-6) value for our answer is  $-6_{10}$  and not  $9_{10}$ . representation, (In unsigned recomplement the answer and attach a – sign.)

### 1.11.6 Binary subtraction using 2's complement

Now let's consider how we would solve our problem of subtracting  $1_{10}$  from  $7_{10}$  using 2's complement.

- 1. First, we need to convert 00012 to its 0111 (7) negative equivalent in 2's complement. <u>- 0001</u> <u>- (1)</u>

- To do this we change all the 1's to 0's 0001 -> 1110 and 0's to 1's and add one to the number. Notice that the most-significant digit is now 1 since the number is negative.

- 3. Next, we add the negative value we 0111 (7) computed to 0111<sub>2</sub>. This gives us a result of + 1111 +(-1) 10110 (?) 10110<sub>2</sub>.

- 4. Notice that our addition caused an overflow bit. Whenever we have an overflow 0111 **(7)** bit in 2's complement, we discard the extra - 0001 - (1) bit. This gives us a final answer of 01102 (or 0110  $6_{10}$ ).

Now let's look at an example where our problem does not generate an overflow bit. We will subtract 7<sub>10</sub> from 1<sub>10</sub> using 1's complement.

| 1. | First, we state our problem in binary.             | 0001 (1)<br><u>- 0111</u> <u>- (7)</u> |

|----|----------------------------------------------------|----------------------------------------|

| 2. | Next, we convert 0111 <sub>2</sub> to its negative | 0001 (1)<br>+ 1000 +(-7)               |

equivalent and add this to 0001<sub>2</sub>. Add 1<sub>2</sub> to it. 1001 (?)

3. This time our result does not cause an overflow, so we do not need to adjust the sum. Notice that our final answer is a negative number since it begins with a 1. Remember that our answer is in 2's complement notation so the correct decimal value for our answer is  $-6_{10}$  and not  $9_{10}$ . representation, unsigned complement the answer 0101 add 1 to it 0110

0001 (1) <u>+ 1001</u> <u>+(-7)</u> 1010 (-6)

# 1.12 QUESTIONS

and attach a – sign.)

- 1. Explain the following terms:

- a. Radix

- b. Decimal number system

- c. Binary number system

- d. Octal number system

- e. Hexadecimal number system

- f. 1's complement

- g. 2's complement

- 2. Convert the following numbers from decimal to binary:

- a. 512

- b. 255

- c. 56.21

- d. 178.71

- e. 223.25

- 3. Convert the following numbers from binary to decimal:

- a. 11011000111

- b. 11111111111

- c. 10101010

- d. 1111.011

- e. 1101101.11

- 4. Convert the following numbers from decimal to octal:

- a. 1024

- b. 800

- c. 789

- d. 826

- e. 425

- 5. Convert the following numbers from octal to decimal:

- a. 145

- b. 512

- c. 677

- d. 177

- e. 1024

- 6. Convert the following numbers from decimal to hexadecimal:

- a. 4096

- b. 975

- c. 1263

- d. 127

- e. 659

- 7. Convert the following numbers from hexadecimal to decimal, binary and octal:

- a. FFFF

- b. A2C3

- c. 8ABC

- d. 1235

- e. 6857

- 8. Perform the following subtraction in binary using 1's complement and 2's complement:

- a. 45 26

- b. 87 96

- c. 128 65

- d. 142 220

- e. 100 56

#### 1.13 FUTHER READING

- Computer Architecture and Organization by William Stallings

- Fundamentals of Computer organization and Design by Sivarama P. Dandamudi

- Digital Electronics An Introduction to Theory and Practice by W H Gothmann

- ❖ Binary Functions and Their Applications by Stormer, H., Beckmann, Martin J

- The Number System by H. A. Thurston

- http://en.wikipedia.org/wiki/Analog\_signal

- http://en.wikipedia.org/wiki/Binary\_numeral\_system

### **CODES**

#### **Unit Structure**

- 2.0 Objectives

- 2.1 Binary codes

- 2.1.1 Binary-coded-decimal Numbers

- 2.2 Geometric Representation of binary Numbers

- 2.3 Distance

- 2.4 Unit-distance codes

- 2.5 Symmetries of the n-cube

- 2.6 Error-detecting and error-correcting codes

- 2.7 Single-error-correcting codes

- 2.8 Ascii code

- 2.9 Ebcdic code

- 2.10 Unicode

- 2.11 Questions

- 2.12 Further Reading

### 3.0 OBJECTIVES

After completing this chapter, you will be able to:

- Understand the binary codes and arithmetic with binary codes.

- Learning the geometrical representation of Binary Numbers.

- Understand the Unit Distance codes.

- Learn the Symmetries Of The N-Cube.

- Work with error handling and error detection codes.

- ❖ Learn the basics about the ASCII, EBCDIC & UNICODE and use the codes in arithmetic.

#### 3.1 BINARY CODES

The binary number system has many advantages and is widely used in digital systems. However, there are times when

binary numbers are not appropriate. Since we think much more readily in terms of decimal numbers than binary numbers, facilities are usually provided so that data can be entered into the system in decimal form, the conversion to binary being performed automatically inside the system. In fact, many computers have been designed which work entirely with decimal numbers. For this to be possible, a scheme for representing each of the 10 decimal digits as a sequence of binary digits must be used.

#### 3.1.1 Binary-Coded-Decimal Numbers

To represent 10 decimal digits, it is necessary to use at least 4 binary digits, since there are 24, or 16, different combinations of 4 binary digits but only 23, or 8, different combinations of 3 binary digits. If 4 binary digits, or **bits**, are used and only one combination of bits is used to represent each decimal digit, there will be six unused or invalid code words. In general, any arbitrary assignment of combinations of bits to digits can be used so that there are 16!/6! or approximately 2.9 X 10<sup>10</sup> possible codes.

#### **Binary Codes:**

| Decimal<br>digit | 8<br><i>b</i> 3 | 4<br>b <sub>2</sub> | 2<br><b>b</b> 1 | 1<br><i>b</i> <sub>0</sub> | 8 | 4 | -2 | -1 | 2 | 4 | 2 | 1 |   | Exc | ess-3 |   |

|------------------|-----------------|---------------------|-----------------|----------------------------|---|---|----|----|---|---|---|---|---|-----|-------|---|

| 0                | 0               | 0                   | 0               | 0                          | 0 | 0 | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0   | 1     | 1 |

| 1                | 0               | 0                   | 0               | 1                          | 0 | 1 | 1  | 1  | 0 | 0 | 0 | 1 | 0 | 1   | 0     | 0 |

| 2                | 0               | 0                   | 1               | 0                          | 0 | 1 | 1  | 0  | 0 | 0 | 1 | 0 | 0 | 1   | 0     | 1 |

| 3                | 0               | 0                   | 1               | 1                          | 0 | 1 | 0  | 1  | 0 | 0 | 1 | 1 | 0 | 1   | 1     | 0 |

| 4                | 0               | 1                   | 0               | 0                          | 0 | 1 | 0  | 0  | 0 | 1 | 0 | 0 | 0 | 1   | 1     | 1 |

| 5                | 0               | 1                   | 0               | 1                          | 1 | 0 | 1  | 1  | 1 | 0 | 1 | 1 | 1 | 0   | 0     | 0 |

| 6                | 0               | 1                   | 1               | 0                          | 1 | 0 | 1  | 0  | 1 | 1 | 0 | 0 | 1 | 0   | 0     | 1 |

| 7                | 0               | 1                   | 1               | 1                          | 1 | 0 | 0  | 1  | 1 | 1 | 0 | 1 | 1 | 0   | 1     | 0 |

| 8                | 1               | 0                   | 0               | 0                          | 1 | 0 | 0  | 0  | 1 | 1 | 1 | 0 | 1 | 0   | 1     | 1 |

| 9                | 1               | 0                   | 0               | 1                          | 1 | 1 | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1   | 0     | 0 |

Only a few of these codes have ever been used in any system, since the arithmetic operations are very difficult in almost all of the possible codes. Several of the more common 4-bit decimal codes are shown in Table. The 8,4,2,1 code is obtained by taking the first 10 binary numbers and assigning them to the corresponding decimal digits. This code is an example of a **weighted code**, since the decimal digits can be determined from the binary digits by forming the sum  $d = 8b_3 + 4b_2 + 2b_1 + b_0$ . The coefficients 8, 4, 2, 1 are known as the **code weights**. The number 462 would be represented as 0100 0110 0010 in the 8,4,2,1 code. It has been shown in that there are only 17 different sets of weights possible for a positively weighted code: (3,3,3,1), (4,2,2,1), (4,3,1,1), (5,2,1,1), (4,3,2,1), (4,4,2,1), (5,2,2,1), (5,3,1,1), (5,3,2,1), (5,4,2,1), (6,2,2,1), (6,3,1,1), (6,3,2,1), (6,4,2,1), (7,3,2,1), (7,4,2,1), (8,4,2,1).

It is also possible to have a weighted code in which some of the weights are negative, as in the 8,4,-2,-1 code shown in Table. This code has the useful property of being **self-complementing**: if a code word is formed by complementing each bit individually (changing 1's to 0's and 0's to 1's), then this new code word represents the 9's complement of the digit to which the original code word corresponds. For example, 0101 represents 3 in the 8,4,-2,-1 code, and 1010 represents 6 in this code. In general, if  $b_i$ denotes the complement of  $b_i$ , then a code is self-complementing if, for any code word  $b_3b_2b_1b_0$  representing a digit  $d_i$ , the code word  $b_3b_2b_1b_0$  represents 9 -  $d_i$ . The 2,4,2,1 code of Table is an example of a self-complementing code having all positive weights, and the excess-3 code is an example of a code which is selfcomplementing but not weighted. The excess-3 code is obtained from the 8,4,2,1 code by adding (using binary arithmetic) 0011 (or 3) to each 8,4,2,1 code word to obtain the corresponding excess-3 code word.

Binary codes using more than 4-bits

| Decimal<br>digit | 2-out-of-5 | <b>Biquinary</b><br>5043210 |

|------------------|------------|-----------------------------|

| 0                | 00011      | 0100001                     |

| 1                | 00101      | 0100010                     |

| 2                | 00110      | 0100100                     |

| 3                | 01001      | 0101000                     |

| 4                | 01010      | 0110000                     |

| 5                | 01100      | 1000001                     |

| 6                | 10001      | 1000010                     |

| 7                | 10010      | 1000100                     |

| 8                | 10100      | 1001000                     |

| 9                | 11000      | 1010000                     |

Although 4 bits are sufficient for representing the decimal digits, it is sometimes expedient to use more than 4 bits in order to achieve arithmetic simplicity or ease in error detection. The 2-out-of-5 code shown in Table has the property that each code word has exactly two 1's. A single error which complements 1 of the bits will always produce an invalid code word and is therefore easily detected. This is an unweighted code. The biquinary code shown in Table is a weighted code in which 2 of the bits specify whether the digit is in the range 0 to 4 or the range 5 to 9 and the other 5 bits identify where in the range the digit occurs.

# 3.2 GEOMETRIC REPRESENTATION OF BINARY NUMBERS

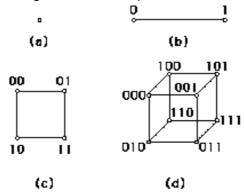

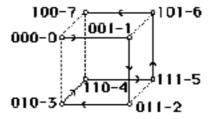

An *n*-bit binary number can be represented by what is called a **point in** *n***space**. To see just what is meant by this, consider the set of 1-bit binary numbers, that is, 0 and 1. This set can be represented by two points in 1-space, i.e., by two points on a line. Such a presentation is called a **1-cube** and is shown in Figure. (A **0-cube** is a single point in 0-space.) Now consider the set of 2-bit binary numbers, that is, 00, 01, 10, 11 (or, decimally, 0, 1, 2, 3). This set can be represented by four points (also called **vertices**, or **nodes**) in 2-space. This representation is called a **2-cube** and is shown in Figure. Note that this figure can be obtained by projecting the 1-cube (i.e., the horizontal line with two points) downward and by prefixing a 0 to 0 and 1 on the original 1-cube and a 1 to 0 and 1 on the projected 1-cube. A similar projection procedure can be followed in obtaining any next-higher-dimensional figure. For example, the representation for the set of 3-bit binary numbers is obtained by projecting the 2-cube representation of Figure c.

Figure: n-Cubes for n = 0, 1, 2, 3: (a) 0-cube; (b) 1-cube; (c) 2-cube; (d) 3-cube.

A 0 is prefixed to the bits on the original 2-cube, and a 1 is prefixed to the bits on the projection of the 2-cube. Thus, the 3-bit representation, or **3-cube**, is shown in Figure d. A more formal statement for the projection method of defining an *n*-cube is as follows:

- 1. A 0-cube is a single point with no designation.

- 2. An *n*-cube is formed by projecting an (*n*-1)-cube. A 0 is prefixed to the designations of the points of the original (*n*-1)-cube, and a 1 is prefixed to the designations of the points of the projected (*n*-1)-cube.

There are  $2^n$  points in an n-cube. A **p-subcube** of an n-cube. (p < n) is defined as a collection of any 2p points which have exactly (n -p) corresponding bits all the same. For example, the points 100, 101, 000, and 001 in the 3-cube (Figure. d) form a 2-subcube, since there are 22 = 4 total points and 3 - 2 = 1 of the bits (the second) is the same for all four points. In general, there are  $(n!2^{n-p})/[(n-p)!p!]$  different p-subcubes in an n-cube, since there are  $(n!2^{n-p})/[(n-p)!p!]$  (number of ways of selecting n things taken n -p at a time) ways in which n -p of the bits may be the same, and there are 2n -p combinations which these bits may take on. For example, there are (3!22)/(2!1!) = 12 1-subcubes (line segments) in a 3-cube, and there are  $(3!2^1)/(1!2!) = 6$  2-subcubes ("squares") in a 3-cube.

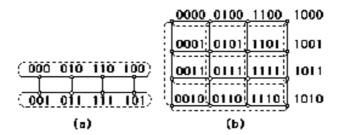

Besides the form shown in Figure, there are two other methods of drawing an *n*-cube which are frequently used. The first of these is shown in Figure 2 for the 3-and 4-cubes. It is seen that these still agree with the projection scheme and are merely a particular way of drawing the cubes. The lines which are dotted are usually omitted for convenience in drawing.

Figure: Alternative representations: (a) 3-cube; (b) 4-cube.

|   |     |           |    |    |    | 00   | 01   | 11    | 10   |

|---|-----|-----------|----|----|----|------|------|-------|------|

|   |     |           |    |    | 00 | 0000 | 0100 | I 100 | 1000 |

|   |     |           |    |    | 01 | 0001 | 0101 | 1101  | 1001 |

|   | 00  | 01<br>010 | 11 | 10 | 11 | 0011 | 0111 | 1111  | 1011 |

| 1 |     | 011       |    |    |    | 0010 | 0110 | 1110  | 1010 |

|   | (a) |           |    |    |    |      | (    | b)    |      |

Figure *n*-Cube maps for n = 3 (a) and n = 4 (b).

If in the representation of Figure we replace each dot by a square area, we have what is known as an **n-cube map**. This representation is shown for the 3- and 4- cubes in Figure Maps will be of considerable use to us later. Notice that the appropriate entry for each cell of the maps of Figure can be determined from the

corresponding row and column labels. It is sometimes convenient to represent the points of an n-cube by the decimal equivalents of their binary designations. For example, Figure shows the 3- and 4-cube maps represented this way. It is of interest to note that, if a point has the decimal equivalent Ni in an n-cube, in an (n + 1)-cube this point and its projection (as defined) become  $N_i$  and  $N_i + 2^n$ .

#### 3.3 DISTANCE

A concept which will be of later use is that of the distance between two points on an n-cube. Briefly, the **distance** between two points on an *n*-cube is simply the number of coordinates (bit positions) in which the binary representations of the two points differ. This is also called the **Hamming distance**.

For example, 10110 and 01101 differ in all but the third coordinate (from left or right). Since the points differ in four coordinates, the distance between them is 4. A more formal definition is as follows: First, define the **mod** 2 **sum** of two bits,  $a ext{ } ext{$

$$0 \ \Box 0 = 0 \ 1 \ \Box 0 = 1$$

$0 \ \Box 1 = 1 \ 1 \ \Box 1 = 0$

That is, the sum is 0 if the 2 bits are alike, and it is 1 if the 2 bits are different. Now consider the binary representations of two points,  $Pi = (an\_1an2 ...a 0)$ ) and Pj = (bn1 bn2 ...b0), on the n-cube. The mod 2 sum of these two points is defined as

$$Pk = Pi \square Pj = (\tilde{an} \square \tilde{bn}1, \tilde{an}2 \square \tilde{bn}2, \dots a0 \square b0)$$

This sum Pk is the binary representation of another point on the n-cube. The number of 1's in the binary representation Pi is defined as the **weight** of Pi and is given the symbol |Pi|. Then the distance (or **metric**) between two points is defined as

$$D(Pi, Pj) = |Pi \square Pj|$$

The distance function satisfies the following three properties:

- D(Pi, Pj) = 0 if and only if Pi = Pj

- D(Pi, Pi) = D(Pi, Pi) > 0 if  $Pi \neq Pi$

- $D(Pi, Pj) + D(Pj, Pk) \ge D(Pi, Pk)$  Triangle inequality

|   |    |     |    |    |    | 00 | 01 | 11 | 10 |

|---|----|-----|----|----|----|----|----|----|----|

|   |    |     |    |    | 00 | 0  | 4  | 12 | 8  |

|   | 00 | nι  | 11 | 10 | 01 | 1  | 5  | 13 | 9  |

| 0 | Õ  | 2   | 6  | 4  | 11 | 3  | 7  | 15 | 11 |

| 1 | 1  | 3   | 7  | 5  | 10 | 2  | 6  | 14 | 10 |

|   |    | (a) |    |    |    |    | (1 | b) |    |

Figure: Decimal labels in *n*-cube maps: (a) 3-cube map; (b) 4-cube map.

To return to the more intuitive approach, since two adjacent points (connected by a single line segment) on an n-cube form a 1-subcube, they differ in exactly one coordinate and thus are distance 1 apart. We see then that, to any two points which are distance D apart, there corresponds a **path** of D connected line segments on the n-cube joining the two points. Furthermore, there will be more than one path of length D connecting the two points (for D > 1 and  $n \ge 2$ ), but there will be no path shorter than length D connecting the two points. A given shortest path connecting the two points, thus, cannot intersect itself, and D + 1 nodes (including the end points) will occur on the path.

## 3.4 UNIT-DISTANCE CODES

In terms of the geometric picture, a code is simply the association of the decimal integers (0,1,2,...) with the points on an n-cube. There are two types of codes which are best described in terms of their geometric properties. These are the so-called **unitdistance codes** and **error-detecting** and **error-correcting codes**. A unit-distance code is simply the association of the decimal integers (0,1,2,...) with the points on a connected path in the n-cube such that the distance is 1 between the point corresponding to any integer i and the point corresponding to integer i + 1 (see Figure). That is, if Pi is the binary-code word for decimal integer i, then we must have

$$D(Pi, Pi + 1) = 1$$

$i = 0, 1, 2, ...$

Unit-distance codes are used in devices for converting analog or continuous signals such as voltages or shaft rotations into binary numbers which represent the magnitude of the signal. Such a device is called an **analog-digital converter**. In any such device there must be boundaries between successive digits, and it is always possible for there to be some misalignment among the different bit positions at such a boundary. For example, if the seventh position is represented by 0111 and the eighth position by 1000, misalignment could cause signals corresponding to 1111 to be generated at the boundary between 7 and 8. If binary numbers were used for such a device, large errors could thus occur. By using a unit-distance code in which adjacent positions differ only in 1 bit, the error due to misalignment can be eliminated.

The highest integer to be encoded may or may not be required to be distance 1 from the code word for 0. If it is distance 1, then the path is closed. Of particular interest is the case of a closed nonintersecting path which goes through all 2n points of the n-cube. In graph theory such a path is known as a (closed) **Hamilton line**. Any unit-distance code associated with such a path is sometimes called a **Gray code**, although this term is usually

reserved for a particular one of these codes. To avoid confusing terminology, we shall refer to a unit-distance code which corresponds to a closed Hamilton line as a **closed** n **code**. This is a unit-distance code containing 2n code words in which the code word for the largest integer (2n - 1) is distance 1 from the code word for the least integer (0). An **open** n **code** is similar except that the code words for the least and largest integer, respectively, are not distance 1 apart. The most useful unit distance code is the Gray code which is shown in Table The attractive feature of this code is the simplicity of the algorithm for translating from the binary number system into the Gray code.

Figure: Path on a 3-cube corresponding to a unitdistance code.

#### **Unit-distance code**

| 0 | 000 |

|---|-----|

| 1 | 001 |

| 2 | 011 |

| 3 | 010 |

| 4 | 110 |

| 5 | 111 |

| 6 | 101 |

| 7 | 100 |

|   |     |

This algorithm is described by the expression  $gi = bi \square bi + 1$

|         |                | Bin            | шу                    |                       |            | ау | y .            |    |  |

|---------|----------------|----------------|-----------------------|-----------------------|------------|----|----------------|----|--|

| Decimal | b <sub>3</sub> | b <sub>3</sub> | <b>b</b> <sub>1</sub> | <i>b</i> <sub>0</sub> | <b>g</b> 3 | ga | g <sub>1</sub> | go |  |

| 0       | 0              | 0              | 0                     | 0                     | 0          | 0  | 0              | 0  |  |

| 1       | 0              | 0              | 0                     | 1                     | 0          | 0  | 0              | 1  |  |

| 2       | 0              | 0              | 1                     | 0                     | 0          | 0  | 1              | 1  |  |

| 3       | 0              | 0              | 1                     | 1                     | 0          | 0  | 1              | 0  |  |

| 4       | 0              | 1              | 0                     | 0                     | 0          | 1  | 1              | 0  |  |

| 5       | 0              | 1              | 0                     | 1                     | 0          | 1  | 1              | 1  |  |

| 6       | 0              | 1              | 1                     | 0                     | 0          | 1  | 0              | 1  |  |

| 7       | 0              | 1              | 1                     | 1                     | 0          | 1  | 0              | 0  |  |

| 8       | 1              | 0              | 0                     | 0                     | 1          | 1  | 0              | 0  |  |

| 9       | 1              | 0              | 0                     | 1                     | 1          | 1  | 0              | 1  |  |

| 10      | 1              | 0              | 1                     | 0                     | 1          | 1  | 1              | 1  |  |

| 11      | 1              | 0              | 1                     | 1                     | 1          | 1  | 1              | 0  |  |

| 12      | 1              | 1              | 0                     | 0                     | 1          | 0  | 1              | 0  |  |

| 13      | 1              | 1              | 0                     | 1                     | 1          | 0  | 1              | 1  |  |

| 14      | 1              | 1              | 1                     | 0                     | 1          | 0  | 0              | 1  |  |

| 15      | 1              | 1              | 1                     | 1                     | 1          | 0  | 0              | 0  |  |

The Gray code

## 3.5 SYMMETRIES OF THE N-CUBE

A **symmetry** of the *n*-cube is defined to be any one-to-one translation of the binary point representations on the *n*-cube which leaves all pairwise distances the same. If we consider the set of binary numbers, we see that there are only two basic translation schemes which leave pairwise distances the same. (1) The bits of one coordinate may be interchanged with the bits of another coordinate in all code words. (2) The bits of one coordinate may be complemented (i.e., change 1's to 0's and 0's to 1's) in all code words. Since there are n! translation schemes possible using (1), and since there are 2n ways in which coordinates may be complemented, there are 2n translation schemes possible using (2). Thus, in all there are 2n(n!) symmetries of the *n*-cube. This means that for any *n*-bit code there are 2n (n!) 1 rather trivial modifications of the original code (in fact, some of these may result in the original code) which can be obtained by interchanging and complementing coordinates. The pairwise distances are the same in all these codes.

It is sometimes desired to enumerate the different types of a class of codes. Two codes are said to be of the same **type** if a symmetry of the n-cube translates one code into the other (i.e., by interchanging and complementing coordinates). As an example, we might ask: What are the types of closed n codes? It turns out that for n < 4 there is just one type, and this is the type of the conventional Gray code. For n = 4, there are nine types. Rather than specify a particular code of each type, we can list these types by specifying the sequence of coordinate changes for a closed path

of that type. On the assumption that the coordinates are numbered (3210), the nine types are shown in Table

TABLE Nine different types of unit-distance 4-bit code

| Туре     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 (Gray) | 0 | 1 | 0 | 2 | 0 | 1 | 0 | 3 | 0 | 1 | 0 | 2 | 0 | 1 | 0 | 3 |

| 2        | 1 | 0 | 1 | 3 | 1 | 0 | 1 | 2 | 0 | 1 | 0 | 3 | 0 | 1 | 0 | 2 |

| 3        | 1 | 0 | 1 | 3 | 0 | 1 | 0 | 2 | 1 | 0 | 1 | 3 | 0 | 1 | 0 | 2 |

| 4        | 1 | 0 | 1 | 3 | 2 | 3 | 1 | 0 | 1 | 3 | 1 | 0 | 2 | 0 | 1 | 3 |

| 5        | 1 | 0 | 1 | 3 | 2 | 0 | 1 | 3 | 1 | 0 | 1 | 3 | 2 | 0 | 1 | 3 |

| 6        | 1 | 0 | 1 | 3 | 2 | 3 | 1 | 3 | 2 | 0 | 1 | 2 | 1 | 3 | 1 | 2 |

| 7        | 1 | 0 | 1 | 3 | 2 | 0 | 2 | 1 | 0 | 2 | 0 | 3 | 0 | 1 | 0 | 2 |

| 8        | 1 | 0 | 1 | 3 | 2 | 1 | 2 | 0 | 1 | 2 | 1 | 3 | 0 | 1 | 0 | 2 |

| 9        | 1 | 0 | 1 | 3 | 2 | 3 | 1 | 0 | 3 | 0 | 2 | 0 | 1 | 2 | 3 | 2 |

## 3.6 ERROR-DETECTING AND ERROR-CORRECTING CODES